隨著物聯(lián)網(wǎng)和智能設(shè)備的快速發(fā)展,嵌入式開發(fā)已成為現(xiàn)代科技領(lǐng)域的核心。本文探討嵌入式開發(fā)VIP電路圖設(shè)計方案,并深入分析計算機軟硬件技術(shù)的協(xié)同開發(fā)過程。

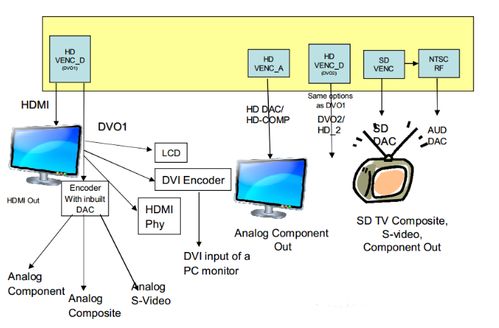

在嵌入式系統(tǒng)設(shè)計中,電路圖設(shè)計是基礎(chǔ)環(huán)節(jié)。VIP電路圖方案強調(diào)高可靠性、低功耗和模塊化設(shè)計。設(shè)計需考慮核心處理器選型,如ARM Cortex系列,結(jié)合外圍電路如電源管理、時鐘電路和復(fù)位電路。傳感器接口(如溫濕度、運動傳感器)的集成需確保信號完整性和抗干擾能力。通過使用EDA工具(如Altium Designer)進行仿真和布局優(yōu)化,可減少電磁干擾并提升系統(tǒng)穩(wěn)定性。VIP方案還包括調(diào)試接口(如JTAG)和通信模塊(如Wi-Fi、藍牙),以支持遠程升級和實時監(jiān)控。

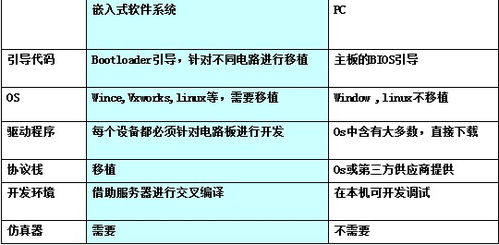

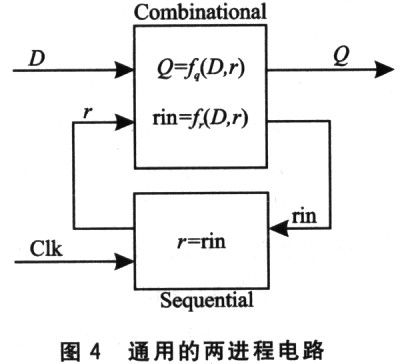

在軟硬件技術(shù)開發(fā)方面,嵌入式開發(fā)強調(diào)軟硬件的緊密集成。硬件部分涉及PCB設(shè)計、元器件選型和測試驗證,確保電路性能滿足需求。軟件層面,使用C/C++或Python編寫固件,結(jié)合實時操作系統(tǒng)(如FreeRTOS)來管理任務(wù)調(diào)度和資源分配。開發(fā)過程中,采用交叉編譯工具鏈在主機上編譯代碼,并通過調(diào)試器部署到目標(biāo)硬件。軟硬件協(xié)同設(shè)計的關(guān)鍵在于驅(qū)動開發(fā)和系統(tǒng)集成,例如,為傳感器編寫驅(qū)動程序,并優(yōu)化算法以實現(xiàn)高效數(shù)據(jù)處理。

嵌入式開發(fā)VIP電路圖方案與計算機軟硬件技術(shù)開發(fā)相輔相成,通過系統(tǒng)化設(shè)計和迭代測試,可構(gòu)建高性能、低成本的嵌入式系統(tǒng),推動智能設(shè)備創(chuàng)新。未來,隨著AI和邊緣計算的融合,這一領(lǐng)域?qū)⒊掷m(xù)演進,開發(fā)者需掌握多學(xué)科知識以應(yīng)對復(fù)雜挑戰(zhàn)。